Please note that the recommended version of Scilab is 2026.1.0. This page might be outdated.

See the recommended documentation of this function

SATURATION

Saturation

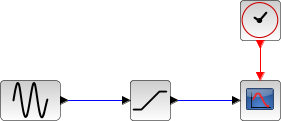

Block Screenshot

Contents

Description

The Saturation block imposes upper and lower bounds on a signal. When the input signal is within the range specified by the Lower limit and Upper limit parameters, the input signal passes through unchanged. When the input signal is outside these bounds, the signal is clipped to the upper or lower bound. When the Lower limit and Upper limit parameters are set to the same value, the block outputs that value.

Parameters

Upper limit

Specify the upper bound on the input signal. When the input signal to the Saturation block is above this value, the output of the block is clipped to this value.

Properties : Type 'vec' of size 1

Lower limit

Specify the lower bound on the input signal. When the input signal to the Saturation block is below this value, the output of the block is clipped to this value.

Properties : Type 'vec' of size 1

Zero crossing

Select to enable zero crossing detection.

Properties : Type 'vec' of size 1

Default properties

always active: no

direct-feedthrough: yes

zero-crossing: yes

mode: yes

regular inputs:

- port 1 : size [1,1] / type 1

regular outputs:

- port 1 : size [1,1] / type 1

number/sizes of activation inputs: 0

number/sizes of activation outputs: 0

continuous-time state: no

discrete-time state: no

object discrete-time state: no

name of computational function: satur

Interfacing function

SCI/modules/scicos_blocks/macros/NonLinear/SATURATION.sci

Computational function

SCI/modules/scicos_blocks/src/c/satur.c (Type 4)

Example

A sine ceilled at 0.6:

| Report an issue | ||

| << RATELIMITER | Discontinuities_pal | Discrete_pal >> |