Please note that the recommended version of Scilab is 2026.0.1. This page might be outdated.

See the recommended documentation of this function

SHIFT

Décalage/Rotation de bits

Aperçu

Contenu

Palette

Description

Ce bloc décale les bits du signal d'entrée. Dans cette opération les chiffres sont déplacés vers la droite ou la gauche. L'utilisateur peut choisir la méthode de décalage qui peut être normale ou cyclique en plaçant le paramètre Shift Type à 0 ou 1. Le nombre et la direction des décalages sont réglés avec le paramètre Number of Bits to Shift Left. Si ce nombre est positif l'entrée est décalée à gauche, sinon elle est décalée à droite.

Quand le paramètre Shift Type est :

0 : un décalage arithmétique est appliqué au signal d'entrée. Dans ce cas, les bits qui sont sortis à l'une ou l'autre extrémité sont perdus. Des zéros sont insérés à droite, dans le cas d'un décalage à gauche;dans le cas d'un décalage à droite, des copies du bit de signe sont insérées à gauche.

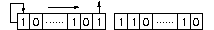

Par exemple un décalage arithmétique à droite de 1 bit donne :

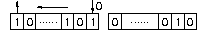

et un décalage arithmétique à gauche donne :

et un décalage arithmétique à gauche donne :

1 : un décalage circulaire est appliqué au signal d'entrée. Dans ce cas, il y a rotation des bits comme si les extrémités de droite et de gauche du registre étaient jointes. La valeur qui est insérée à droite pendant un décalage à gauche est la valeur qui est décalée et sortie à gauche et vice et versa.

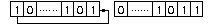

Par exemple une rotation à droite de 1 bit donne :

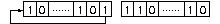

et une rotation à gauche :

et une rotation à gauche :

Le registre à décalage effectue une multiplication par 2n

(décalage à gauche arithmétique) ou une division entière par 2n

(décalage à droite arithmétique), où n est le nombre de décalages.

Il peut également être utilisé pour sérialiser des données ou créer une mémoire tampon.

Types de données

Le bloc supporte les types de données suivants :

Entrée : scalaire. Tout type entier de Scilab (paramètre Data Type).

Sortie : scalaire. Même type que l'entrée.

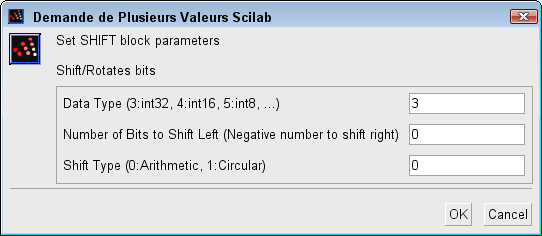

Boîte de dialogue

Data Type (3:int32, 4:int16, 5:int8, ...)

Indique le type de données en entrée : entre 3 et 8.

Propriétés : Type 'vec' de taille 1.

Number of Bits to Shift Left (Negative number to shift right)

Indique le nombre de bits du signal d'entrée à décaler. Une valeur positive indique un décalage à gauche, une valeur négative un décalage à droite. L'indice doit être, quand le type est :

int32 or uint32 : positif et inférieur à 32.

int16 or uint16 : positif et inférieur à 16.

int8 or uint8 : positif et inférieur à 8.

Propriétés : Type 'vec' de taille 1.

Shift Type (0:Arithmetic, 1:Circular)

O ou 1. Indique la règle utilisée pour le décalage des bits. Il peut être arithmétique ou circulaire. Voir la description pour plus d'information. Quand il est égal à :

0, un décalage arithmétique est appliqué au signal d'entrée.

1, un décalage circulaire est appliqué au signal d'entrée.

Voir la description pour plus d'information.

Propriétés : Type 'vec' de taille 1.

Propriétés par défaut

always active: non

direct-feedthrough: oui

zero-crossing: non

mode: non

regular inputs:

- port 1 : size [-1,-2] / type 3

regular outputs:

- port 1 : size [-1,-2] / type 3

number/sizes of activation inputs: 0

number/sizes of activation outputs: 0

continuous-time state: non

discrete-time state: non

object discrete-time state: non

name of computational function: shift_32_LA

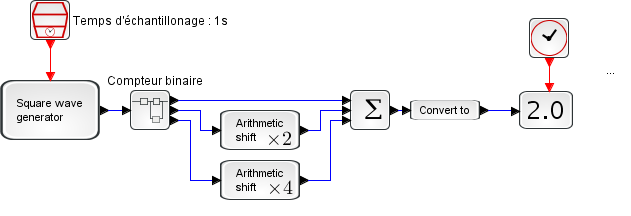

Exemple

Dans cet exemple le Super bloc est un compteur binaire 3 bits. De façon à obtenir les données décimales correspondantes,

les sorties Q1

et Q2 du compteur sont respectivement

décalées à gauche de un et de deux bits. Finalement la sortie Q0

et les sorties décalées sont additionnées.

Pour bien voir l'évolution, mettre le paramètre Mise à l'échelle temps réel à 0.5 s dans le sous-menu Configurer du menu Simulation. Ouvrir cet exemple dans Xcos

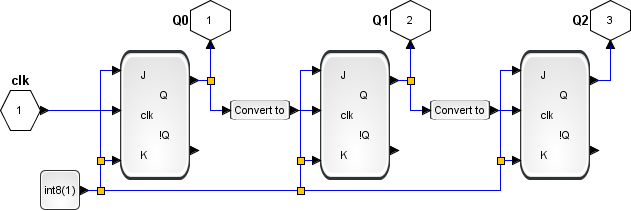

Ci-dessous le détail du compteur binaire.

Fonction d'interfaçage

Fonctions de calcul

SCI/modules/scicos_blocks/src/c/shift_32_LA.c

SCI/modules/scicos_blocks/src/c/shift_32_LC.c

SCI/modules/scicos_blocks/src/c/shift_32_RA.c

SCI/modules/scicos_blocks/src/c/shift_u32_RA.c

SCI/modules/scicos_blocks/src/c/shift_32_RC.c

SCI/modules/scicos_blocks/src/c/shift_16_LA.c

SCI/modules/scicos_blocks/src/c/shift_16_LC.c

SCI/modules/scicos_blocks/src/c/shift_16_RA.c

SCI/modules/scicos_blocks/src/c/shift_u16_RA.c

SCI/modules/scicos_blocks/src/c/shift_16_RC.c

SCI/modules/scicos_blocks/src/c/shift_8_LA.c

SCI/modules/scicos_blocks/src/c/shift_8_LC.c

SCI/modules/scicos_blocks/src/c/shift_8_RA.c

SCI/modules/scicos_blocks/src/c/shift_u8_RA.c

SCI/modules/scicos_blocks/src/c/shift_8_RC.c

Auteurs

Fady NASSIF - INRIA

| << LOGIC | Palette Entier | SRFLIPFLOP >> |