TIME_DELAY

Retard pur

Aperçu

Contenu

Description

Le bloc Retard pur retarde l'entrée d'un temps spécifié. Il peut être utilisé pour simuler un retard. Au début de la simulation la sortie du bloc est égale au paramètre Initial input jusqu'à ce que le temps de simulation dépasse le paramètre de temps Delay, ensuite le bloc commence à générer l'entrée retardée.

Le paramètre Time delay ne doit pas être négatif.

Paramètres

Delay

La quantité de temps de simulation dont le signal d'entrée est retardé avant d'être propagé en sortie. La valeur doit être non-négative.

Propriétés Type 'vec' de taille 1

Initial input

La sortie générée par le bloc entre le début de la simulation et le temps Delay.

Propriétés Type 'vec' de taille 1

Buffer size

L'allocation mémoire initiale du nombre de points à mémoriser.

Propriétés Type 'vec' de taille 1

Propriétés par défaut

always active: non

direct-feedthrough: non

zero-crossing: non

mode: non

regular inputs:

- port 1 : size [1,1] / type 1

regular outputs:

- port 1 : size [1,1] / type 1

number/sizes of activation inputs: 0

number/sizes of activation outputs: 0

continuous-time state: non

discrete-time state: non

object discrete-time state: non

name of computational function: time_delay

Fonction d'interfaçage

SCI/modules/scicos_blocks/macros/Linear/TIME_DELAY.sci

Fonction de calcul

SCI/modules/scicos_blocks/src/c/time_delay.c (Type 4)

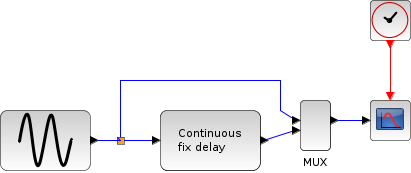

Exemple

| Report an issue | ||

| << TCLSS | Palette Systèmes à temps continu | VARIABLE_DELAY >> |