Please note that the recommended version of Scilab is 2026.1.0. This page might be outdated.

See the recommended documentation of this function

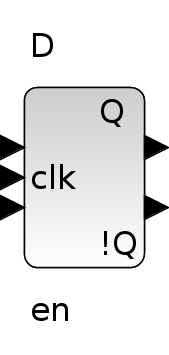

DFLIPFLOP

D flip-flop

Block Screenshot

Description

That block outputs on Q its input state (D) when the enable input (en) is set and on the rising edge of the clock input (clk). The !Q output is the logical negation of Q. This flip-flop is also known as a delay flip-flop because the state of the input is modified only at the next rising edge of the clock.

The D flip-flop is used as a basic cell of shift-registers.

The truth table of this block is the following:

| clk | en | D | Qn | !Qn |

|---|---|---|---|---|

| ↑ | 0 | X | Qn-1 | !Qn-1 |

| ↑ | 1 | 0 | 0 | 1 |

| ↑ | 1 | 1 | 1 | 0 |

| Non-Rising | X | X | Qn-1 | !Qn-1 |

where

X

stands for "indifferent" and

Qn-1

is the previous output state of

Qn

.

Data types

The block supports the following types :

Inputs:

D: scalar. Scilab's int8 data type only.

en: scalar. Scilab's real double.

clk: scalar. Scilab's real double.

A positive input is considered as logical 1, a negative or a null input as logical 0.

Outputs : scalar. Scilab's int8 data type.

Default properties

always active: no

direct-feedthrough: yes

zero-crossing: no

mode: no

regular inputs:

- port 1 : size [1,1] / type 5

- port 2 : size [1,1] / type 1

- port 3 : size [1,1] / type 1

regular outputs:

- port 1 : size [1,1] / type 5

- port 2 : size [1,1] / type 5

number/sizes of activation inputs: 0

number/sizes of activation outputs: 0

continuous-time state: no

discrete-time state: no

object discrete-time state: no

name of computational function: csuper

Interfacing function

SCI/modules/scicos_blocks/macros/IntegerOp/DFLIPFLOP.sci

See also

- DLATCH — D latch flip-flop

- SRFLIPFLOP — SR flip-flop

- JKFLIPFLOP — JK flip-flop

| Report an issue | ||

| << CONVERT | Integer palette | DLATCH >> |