Please note that the recommended version of Scilab is 2026.0.1. This page might be outdated.

See the recommended documentation of this function

OUTIMPL_f

Port de sortie implicite

Aperçu

Contenu

Description

Ce bloc représente un port de sortie implicite. Il doit seulement être utilisé à l'intérieur des Super Bloc Xcos et être connecté sur une sortie implicite dans le sous-système.

Ce bloc est une liaison de signal d'un système dans un sous-système. Dans un Super Bloc, les ports de sortie implicites doivent être numérotés de 1 au nombre de ports de sortie réguliers. Vous pouvez l'initialiser avec le paramètre Port number.

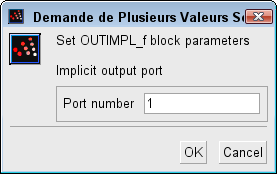

Paramètres

Port number

Un entier définissant le numéro de port.

Propriétés : Type 'vec' de taille 1.

Propriétés par défaut

always active: non

direct-feedthrough: non

zero-crossing: non

mode: non

regular inputs:

- port 1 : size [-1,1] / type 1

number/sizes of activation inputs: 0

number/sizes of activation outputs: 0

continuous-time state: non

discrete-time state: non

object discrete-time state: non

name of computational function: outimpl

Exemple

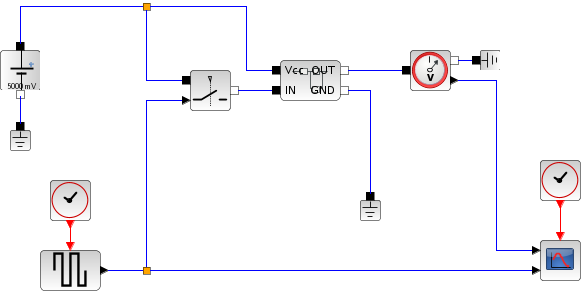

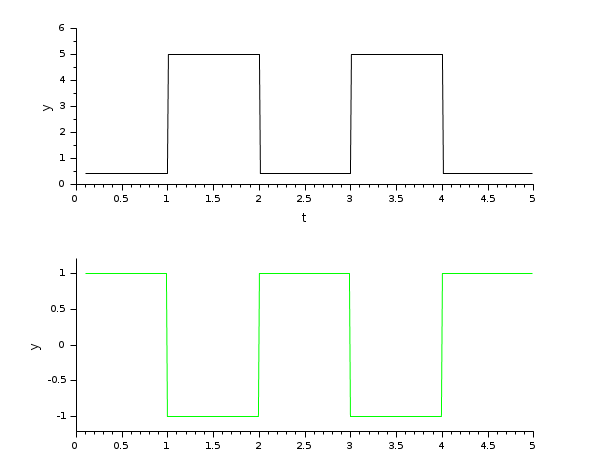

Dans l'exemple suivant le Super bloc est un simple commutateur à transistor.

La figure suivante montre l'utilisation du Super bloc et la sortie résultante lorsque son entrée est basculée entre les potentiels GND et Vcc. Vous pouvez voir sur la sortie l'effet de la tension de saturation du transistor (sortie minimale = 0.4 Volt).

Fonction d'interfaçage

SCI/modules/scicos_blocks/macros/Sinks/OUTIMPL_f.sci

| Report an issue | ||

| << OUT_f | Palette Port & Sous-systèmes | Signal processing palette >> |