Please note that the recommended version of Scilab is 2026.0.1. This page might be outdated.

See the recommended documentation of this function

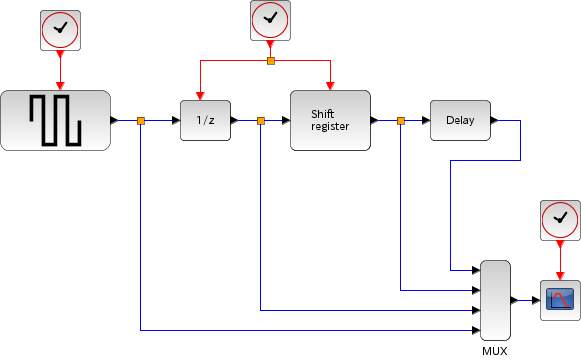

DELAY_f

Discrete time delay

Block Screenshot

Contents

Palette

Description

This compiled super-block implements a discretized delay. It is built with a shift register and a clock. The value of the delay is given by the discretization time step multiplied by the number-1 of state of the register.

Dialog box

Discretization time step

Set the time period of the integrated clock.

Properties : Type 'vec' of size 1.

Register initial state

Set the length and the initial conditions of the register.

Properties : Type 'vec' of size -1.

Default properties

always active: no

direct-feedthrough: no

zero-crossing: no

mode: no

regular inputs:

- port 1 : size [1,1] / type 1

regular outputs:

- port 1 : size [1,1] / type 1

number/sizes of activation inputs: 0

number/sizes of activation outputs: 0

continuous-time state: no

discrete-time state: no

object discrete-time state: no

name of computational function: csuper

Example

Interfacing function

SCI/modules/scicos_blocks/macros/Linear/DELAY_f.sci

| Report an issue | ||

| << DELAYV_f | Discrete time systems palette | DLR >> |