OUTIMPL_f

Output implicit port

Block Screenshot

Description

This block represents a regular implicit port. It must only be used inside a Xcos Super Block and be connected to an implicit output of an internal implicit output in the sub-system.

This block is a signal link from outside of a system into a sub-system. In a Super Block, the implicit's output ports must be numbered from 1 to the total number of implicit's output ports. You can set it with the Port number parameter.

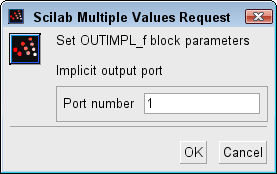

Parameters

Port number

An integer defining the port number.

Properties : Type 'vec' of size 1.

Default properties

always active: no

direct-feedthrough: no

zero-crossing: no

mode: no

regular inputs:

- port 1 : size [-1,1] / type 1

number/sizes of activation inputs: 0

number/sizes of activation outputs: 0

continuous-time state: no

discrete-time state: no

object discrete-time state: no

name of computational function: outimpl

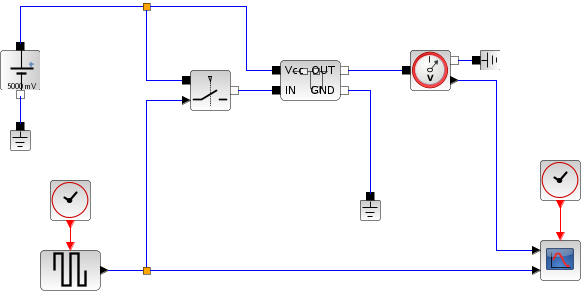

Example

In the following example the Super block is a basic transistor switch.

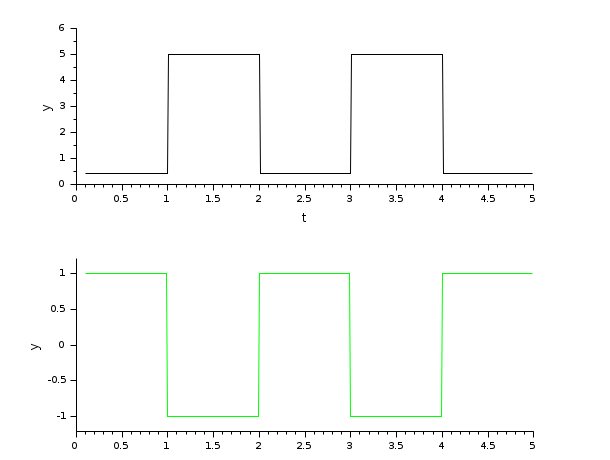

The following figure shows the output of the bloc :

Interfacing function

SCI/modules/scicos_blocks/macros/Sinks/OUTIMPL_f.sci

| Report an issue | ||

| << OUT_f | Portaction_pal | Signalprocessing_pal >> |