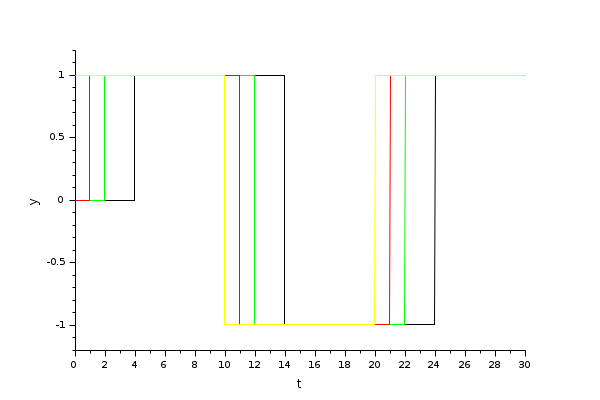

DELAY_f

Discrete time delay

Block Screenshot

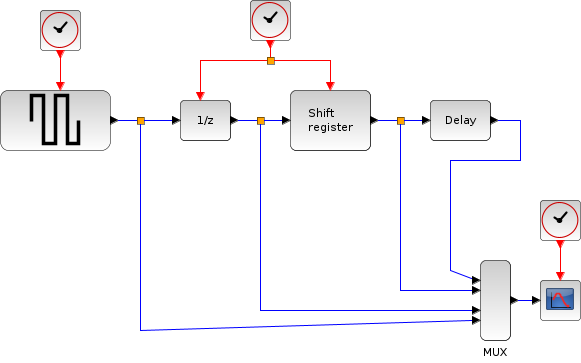

Description

This compiled super-block implements a discretized delay. It is built with a shift register and a clock. The value of the delay is given by the discretization time step multiplied by the number-1 of state of the register.

![\left\{

\begin{array}{l l}

T_0=length(Register) \\

y(t) = Register(n) & \text{when}\ t < nT_0 \\

y(t) = x(n*(T - T_0)) & \text{when}\ t\in[n;n+1]*(T - T_0)

\end{array}

\right.](/docs/2024.1.0/pt_BR/_LaTeX_DELAY_f.xml_1.png)

.

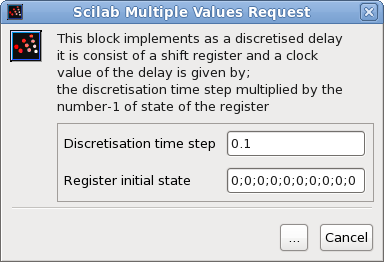

Parameters

Discretization time step

Set the time period of the integrated clock.

Properties : Type 'vec' of size 1.

Register initial state

Set the length and the initial conditions of the register.

Properties : Type 'vec' of size -1.

Default properties

always active: no

direct-feedthrough: no

zero-crossing: no

mode: no

regular inputs:

- port 1 : size [1,1] / type 1

regular outputs:

- port 1 : size [1,1] / type 1

number/sizes of activation inputs: 0

number/sizes of activation outputs: 0

continuous-time state: no

discrete-time state: no

object discrete-time state: no

name of computational function: csuper

Interfacing function

SCI/modules/scicos_blocks/macros/Linear/DELAY_f.sci

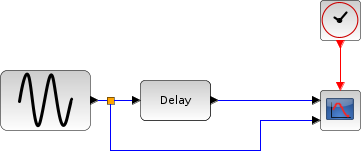

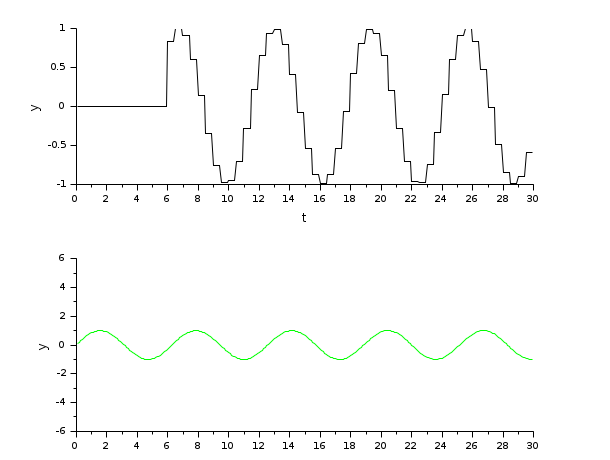

Example

| Report an issue | ||

| << Discrete_pal | Discrete_pal | DELAYV_f >> |