Please note that the recommended version of Scilab is 2026.0.1. This page might be outdated.

See the recommended documentation of this function

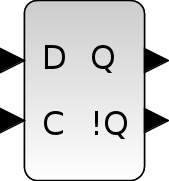

DLATCH

Bascule D transparente

Aperçu

Contenu

Description

Ce bloc copie son état d'entrée (D) sur la sortie (Q) quand l'entrée de validation (C) est haute et dans cette configuration, il apparaît comme transparent. La sortie !Q est la négation logique de Q.

Quand l'entrée de validation devient basse, la sortie garde son état antérieur et agit comme une mémoire.

Ce bloc peut être typiquement utilisé dans les ports d'entrée/sortie.

La table de vérité du bloc est la suivante :

| C | D | Qn | !Qn | |

|---|---|---|---|---|

| 0 | x | Qn-1 | !Qn-1 | inchangé |

| 1 | 0 | 0 | 1 | Remise à 0 |

| 1 | 1 | 1 | 0 | Mise à 1 |

où X signifie "indifférent" et

Qn-1

l'état antérieur de

Qn.

Types de données

Le bloc supporte les types suivants :

Entrées :

D : scalaire. Seulement le type entier int8 de Scilab.

C : scalaire. Le type réel double de Scilab.

Une entrée positive est considérée comme un 1 logique, une entrée négative ou nulle comme un 0 logique.

Sorties : scalaires. Type int8 de Scilab.

Propriétés par défaut

always active: non

direct-feedthrough: oui

zero-crossing: non

mode: non

regular inputs:

- port 1 : size [1,1] / type 5

- port 2 : size [1,1] / type -1

regular outputs:

- port 1 : size [1,1] / type 5

- port 2 : size [1,1] / type 5

number/sizes of activation inputs: 0

number/sizes of activation outputs: 0

continuous-time state: non

discrete-time state: non

object discrete-time state: non

name of computational function: csuper

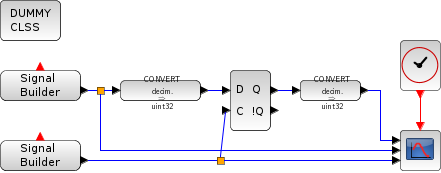

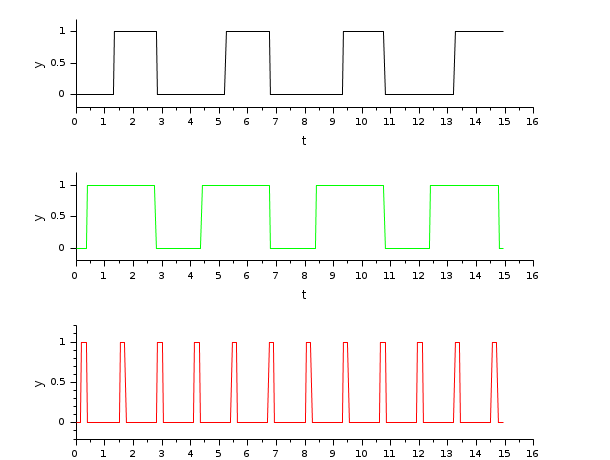

Exemple

La figure suivante montre un cas simple d'utilisation du bloc DLATCH avec son chronogramme.

Fonction d'interfaçage

SCI/modules/scicos_blocks/macros/IntegerOp/DLATCH.sci

Voir aussi

- DFLIPFLOP — Bascule D

- SRFLIPFLOP — Bascule SR

- JKFLIPFLOP — Bascule JK

| Report an issue | ||

| << DFLIPFLOP | Palette Entier | EXTRACTBITS >> |