Please note that the recommended version of Scilab is 2026.0.1. This page might be outdated.

See the recommended documentation of this function

LOGIC

Logique combinatoire

Aperçu

Contenu

Description

Le bloc implémente une table de vérité standard pour la modélisation de tableaux de programmation, de circuits digitaux et de toute autre expression booléenne.

L'utilisateur doit spécifier une matrice qui définit toutes les sorties de bloc possibles dans le champ Truth Table. En conséquence, le nombre de lignes doit être une puissance de deux. Chaque ligne de la matrice contient une combinaison logique des éléments d'entrée

L'initialisation du paramètre Truth Table définit le nombre d'entrées et de sorties du bloc de la façon suivante :

Le nombre d'entrées est défini par la relation :

Nombre de lignes = 2(nombre d'entrées)

Le nombre de sorties est égal au nombre de colonnes de la matrice.

Ce bloc peut être activé par un événement d'entrée implicite ou hériter de l'horloge à partir de l'entrée régulière (paramètre Accepts inherited events).

Types de données

Le bloc supporte les types de données suivants :

Entrée : scalaire. Tout type entier de Scilab.

Une entrée positive est considérée comme un 1 logique, une entrée négative ou nulle est considérée comme un 0 logique.

Sortie : scalaire. Même type que l'entrée.

Paramètres

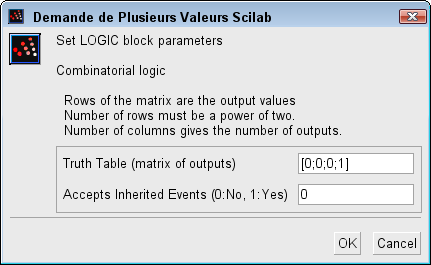

Truth Table

La matrice des sorties. Les éléments doivent être 0 ou 1. Pour plus d'information voir la partie description.

Propriétés : Type 'mat' de taille [-1,-2].

Accepts Inherited Events (0:No, 1:Yes)

Spécifie si l'horloge est héritée ou pas. 0 ou 1

Propriétés : Type 'vec' de taille 1.

Propriétés par défaut

always active: non

direct-feedthrough: oui

zero-crossing: non

mode: non

regular inputs:

- port 1 : size [1,1] / type 5

- port 2 : size [1,1] / type 5

regular outputs:

- port 1 : size [1,1] / type 5

number/sizes of activation inputs: 1

number/sizes of activation outputs: 0

continuous-time state: non

discrete-time state: non

object discrete-time state: non

name of computational function: logic

Exemples

Exemple 1

L'exemple le plus simple à considérer est le OR. Dans ce cas nous avons deux entrées et seulement une sortie. La table de vérité pour cet exemple est :

| input 1 | input 2 | output |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

et le paramètre Truth Table est écrit :

[0;1;1;1]

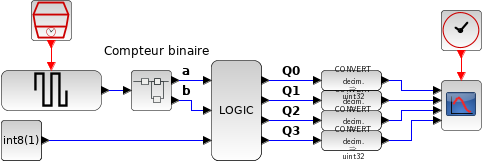

Exemple 2

Cet exemple montre l'utilisation du bloc LOGIC en tant que démultiplexeur. Le but est d'envoyer l'entrée constante égale

à vrai sur une des quatre sorties en accord avec l'état des deux entrées de sélection :

a et b.

La table de vérité est la suivante :

| Constant | a | b | Q0 | Q1 | Q2 | Q3 |

| 0 | X | X | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | 1 |

où X signifie "indifférent".

Pour mettre cette table dans le paramètre Truth Table, on peut simplement écrire :

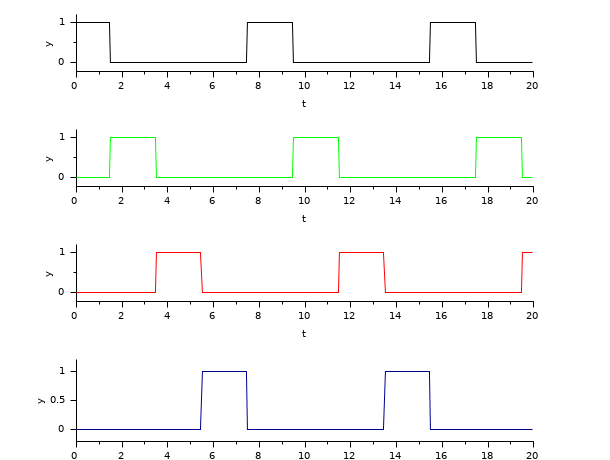

La figure suivante montre les sorties

Q0

à Q3

obtenues pendant la simulation quand les entrées

a

et b

de sélection du bloc sont générées par un compteur binaire.

Fonction d'interfaçage

SCI/modules/scicos_blocks/macros/IntegerOp/LOGIC.sci

Fonction de calcul

SCI/modules/scicos_blocks/src/c/logic.c

Voir aussi

- BITSET — Positionne un bit à 1

- BITCLEAR — Positionne un bit à 0

- LOGICAL_OP — Opération logique

- EXTRACTBITS — Extraction de bits

| Report an issue | ||

| << JKFLIPFLOP | Palette Entier | SHIFT >> |