REGISTER

Registre à décalage

Aperçu

Contenu

Description

Ce bloc réalise un registre à décalage. A chaque activation, le contenu du registre est décalé d'un pas.

Paramètres

Register initial condition

Un vecteur colonne. Il contient l'état initial du registre.

Propriétés : Type 'vec' de taille -1

Datatype

Ce bloc supporte tous les types de données en plus du type complexe.

Propriétés : Type 'vec' de taille -1

Propriétés par défaut

always active: non

direct-feedthrough: non

zero-crossing: non

mode: non

regular inputs:

- port 1 : size [1,1] / type 1

regular outputs:

- port 1 : size [1,1] / type 1

number/sizes of activation inputs: 1

number/sizes of activation outputs: 0

continuous-time state: non

discrete-time state: oui

object discrete-time state: non

name of computational function: delay4

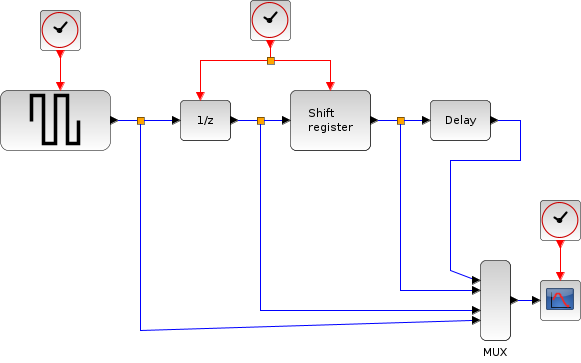

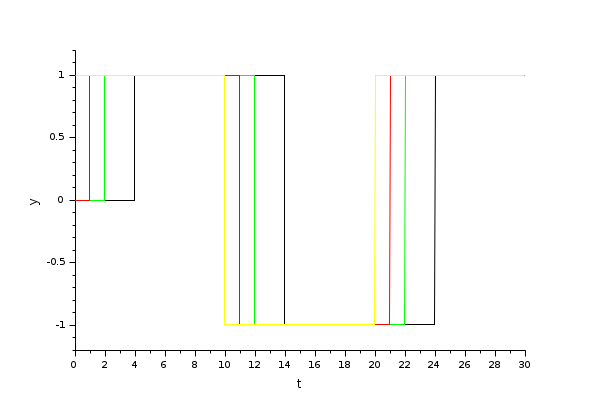

Exemple

Fonction d'interfaçage

SCI/modules/scicos_blocks/macros/Linear/REGISTER.sci

Fonctions de calcul

- SCI/modules/scicos_blocks/src/c/delay4_i32.c

- SCI/modules/scicos_blocks/src/c/delay4_i16.c

- SCI/modules/scicos_blocks/src/c/delay4_i8.c

- SCI/modules/scicos_blocks/src/c/delay4_ui32.c

- SCI/modules/scicos_blocks/src/c/delay4_ui16.c

- SCI/modules/scicos_blocks/src/c/delay4_ui8.c

| Report an issue | ||

| << DOLLAR_f | Palette Systèmes à temps discret | Palette Electrique >> |