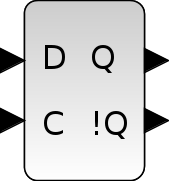

DLATCH

D latch flip-flop

Block Screenshot

Description

This block copies its input state (D) on the output (Q) when the enable input (C) is high and in this configuration it appears as transparent. The !Q output is the logical negation of Q

When the enable input goes low, the output keeps its previous state and acts like a memory.

This block can be typically used in I/O ports.

The truth table of the block is the following ones:

| C | D | Qn | !Qn | |

|---|---|---|---|---|

| 0 | x | Qn-1 | !Qn-1 | No changes |

| 1 | 0 | 0 | 1 | Reset |

| 1 | 1 | 1 | 0 | Set |

where

x

means "indifferent" and

Qn-1

the previous state of

Qn.

Data types

The block supports the following types :

Inputs:

D: scalar. Scilab's int8 data type only.

C: scalar. Scilab's real double.

A positive input is considered as logical 1, a negative or a null input as logical 0.

Outputs: scalar. Scilab's int8 data type.

Default properties

always active: no

direct-feedthrough: yes

zero-crossing: no

mode: no

regular inputs:

- port 1 : size [1,1] / type 5

- port 2 : size [1,1] / type -1

regular outputs:

- port 1 : size [1,1] / type 5

- port 2 : size [1,1] / type 5

number/sizes of activation inputs: 0

number/sizes of activation outputs: 0

continuous-time state: no

discrete-time state: no

object discrete-time state: no

name of computational function: csuper

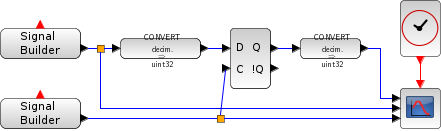

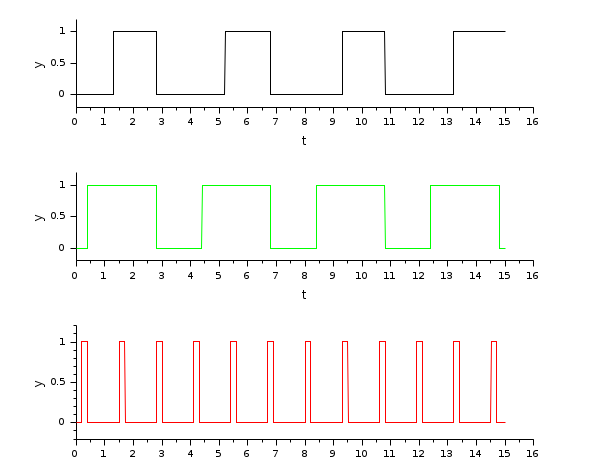

Example

The following figure shows a simple use case of the DLATCH block with its timing diagram.

Interfacing function

SCI/modules/scicos_blocks/macros/IntegerOp/DLATCH.sci

See also

- DFLIPFLOP — D flip-flop

- SRFLIPFLOP — SR flip-flop

- JKFLIPFLOP — JK flip-flop

| Report an issue | ||

| << DFLIPFLOP | Integer palette | EXTRACTBITS >> |